Chips

Asked on 2025-09-12

1 search

Apple's WWDC sessions often cover a wide range of topics related to their hardware and software advancements, including their custom silicon chips. For instance, in the session titled "Optimize CPU performance with Instruments" from WWDC 2025, Apple discusses the architecture of their silicon processors, highlighting features like pipelining and instruction-level parallelism, which are crucial for optimizing CPU performance (Optimize CPU performance with Instruments).

Additionally, the session "Bring your machine learning and AI models to Apple silicon" from WWDC 2024 explores how Apple's silicon, particularly their GPUs, can be leveraged for machine learning tasks, showcasing the conversion of large language models to run efficiently on Apple silicon (Bring your machine learning and AI models to Apple silicon).

These sessions reflect Apple's focus on maximizing the performance and efficiency of their custom chips, which are integral to their ecosystem. If you have specific questions about Apple's silicon or related technologies, feel free to ask!

Optimize CPU performance with Instruments

Learn how to optimize your app for Apple silicon with two new hardware-assisted tools in Instruments. We’ll start by covering how to profile your app, then dive deeper by showing every single function called with Processor Trace. We’ll also discuss how to use CPU Counters’ modes to analyze your code for CPU bottlenecks.

Unlock GPU computing with WebGPU

Learn how the WebGPU API provides safe access to GPU devices for graphics and general-purpose computation. We’ll also explore the WGSL shading language to write GPU programs. And we’ll dive into best practices to achieve optimal performance while using minimal power across desktop and mobile devices.

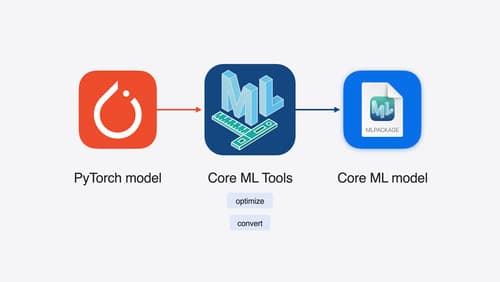

Bring your machine learning and AI models to Apple silicon

Learn how to optimize your machine learning and AI models to leverage the power of Apple silicon. Review model conversion workflows to prepare your models for on-device deployment. Understand model compression techniques that are compatible with Apple silicon, and at what stages in your model deployment workflow you can apply them. We’ll also explore the tradeoffs between storage size, latency, power usage and accuracy.